Hi,

I have a basic question that I can´t get my head around.

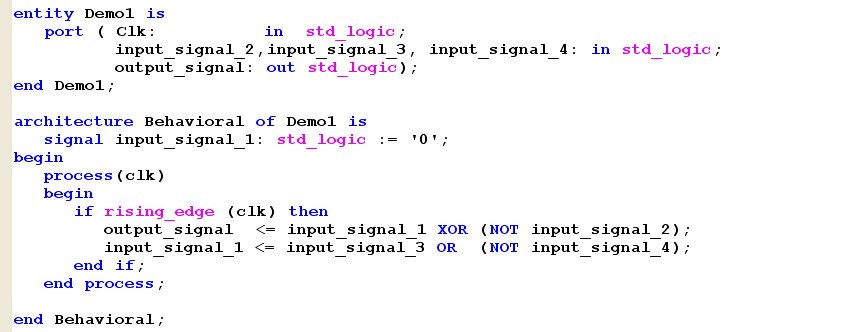

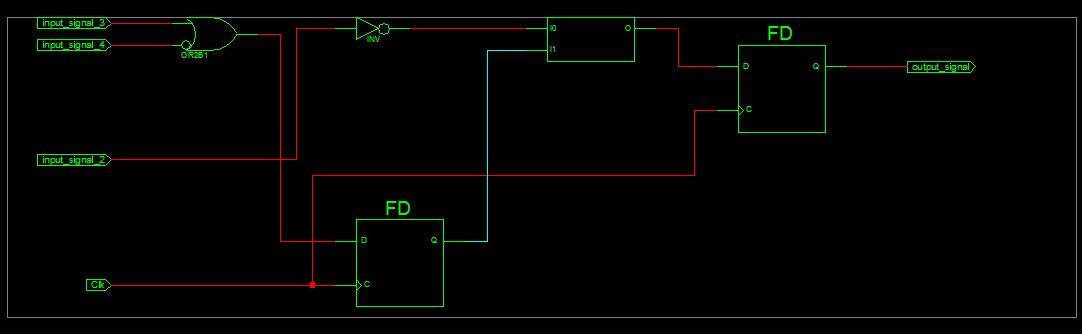

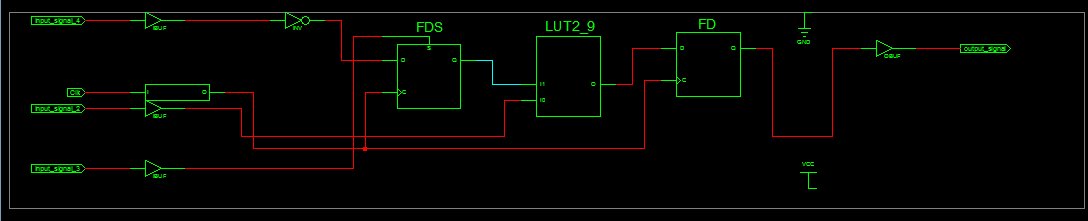

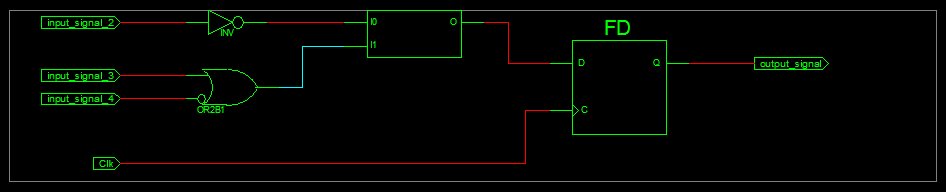

In the following process I have 1 signal which is mapped to an output and 4 inputs.

process(clk)

begin

if rising_edge (clk)

ouput_signal <= input_signal_1 AND (NOT input_signal_2);

input_signal_1 <= input_signal_3 OR (NOT input_signal4);

end if;

end process;

My question is, When the clk edge arrives, does the process takes the values of each of the signals at that moment in time and do the calculations. In which case the changing of input_signal_1 would not affect the state of output_signal. (Is it tue to say that output_signal already has the result of the logic statement and that it will be latched on the clock edge?)

OR

If for example input_signal_3 had changed since the last clock edge and lets say input_signal_1 then changed 3 ns later...could the changing of input_signal_1 have a negative effect when output_signal is being assigned. i.e. input_signal 1 could be in the process of changing, or could have already changed or may not have changed yet.

Maybe the process above is bad design practise? But I just want to have a better understanding of what would actually happen.

I hope I have explained it clearly enough. If not please let me know.

Thanks

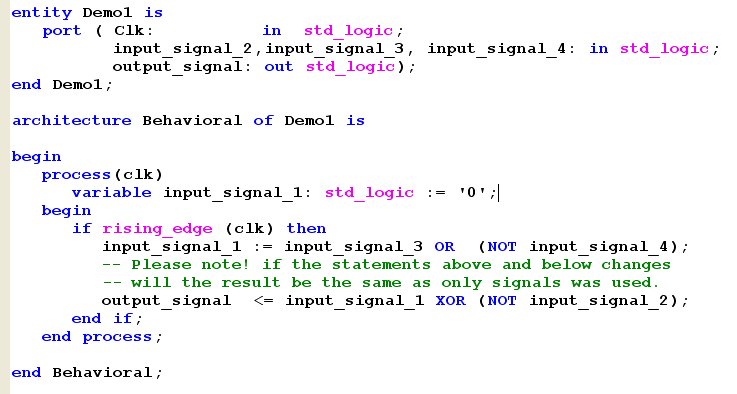

I have a basic question that I can´t get my head around.

In the following process I have 1 signal which is mapped to an output and 4 inputs.

process(clk)

begin

if rising_edge (clk)

ouput_signal <= input_signal_1 AND (NOT input_signal_2);

input_signal_1 <= input_signal_3 OR (NOT input_signal4);

end if;

end process;

My question is, When the clk edge arrives, does the process takes the values of each of the signals at that moment in time and do the calculations. In which case the changing of input_signal_1 would not affect the state of output_signal. (Is it tue to say that output_signal already has the result of the logic statement and that it will be latched on the clock edge?)

OR

If for example input_signal_3 had changed since the last clock edge and lets say input_signal_1 then changed 3 ns later...could the changing of input_signal_1 have a negative effect when output_signal is being assigned. i.e. input_signal 1 could be in the process of changing, or could have already changed or may not have changed yet.

Maybe the process above is bad design practise? But I just want to have a better understanding of what would actually happen.

I hope I have explained it clearly enough. If not please let me know.

Thanks