A

Amit

hello group,

I have written two small vhdl code and now I am asked the following

questions, please just point where I can find some reading about it to

answer them. (I am using xilinx ise)

regards,

amit

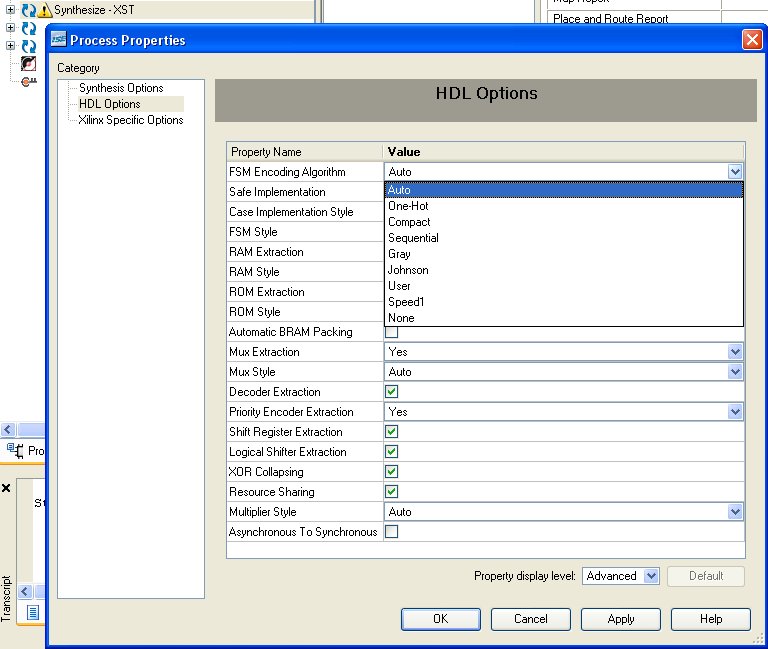

Different synthesis tools use different styles to synthesize the state

machines.

Whatstyle does XST use to synthesize the state machine that you

coded?

Is there any way to force the tool to use specific options for

synthesizing state machines?

I have written two small vhdl code and now I am asked the following

questions, please just point where I can find some reading about it to

answer them. (I am using xilinx ise)

regards,

amit

Different synthesis tools use different styles to synthesize the state

machines.

Whatstyle does XST use to synthesize the state machine that you

coded?

Is there any way to force the tool to use specific options for

synthesizing state machines?