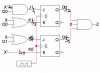

Good Morning, guys. Noob here. Please help me to code this circuit in vhdl. This exercise is already done but its bugging me like crazy. This is my code for this circuit.

library IEEE;

use IEEE.std_logic_1164.all;

----- OR GATE -----

entity orgate is

port( a,b : in bit; c : out bit);

end orgate;

architecture orarchi of orgate is

begin

c <= a or b;

end orarchi;

----- AND GATE (2-INPUT) -----

entity andgate2 is

port( a,b : in bit; c : out bit);

end andgate2;

architecture andarchi2 of andgate2 is

begin

c <= a and b;

end andarchi2;

----- AND GATE (3-INPUT) -----

entity andgate3 is

port( a,b,c : in bit; d : out bit);

end andgate3;

architecture andarchi3 of andgate3 is

begin

d <= a and b and c;

end andarchi3;

----- INVERTER -----

entity inv is

port( a : in bit; b : out bit);

end inv;

architecture invarchi of inv is

begin

b <= not a;

end invarchi;

----- JK FLIP FLOP -----

entity jk is

port( clk,j,k : in bit; q : out bit);

end jk;

architecture jkarchi of jk is

begin

process(clk,j,k)

variable temp : bit;

begin

if(clk = '1' and clk'event) then

if(j = '0' and k = '0') then

temp := temp;

elsif(j = '0' and k = '1') then

temp := '0';

elsif(j = '1' and k = '0') then

temp := '1';

elsif(j = '1' and k = '1') then

temp := not temp;

end if;

q <= temp;

else

temp := temp;

end if;

end process;

end jkarchi;

--!--!--!--!--!---!--!--!--!--!

--! CIRCUIT PORT MAPPING --!--!

--!--!--!--!--!---!--!--!--!--!

entity circ_2 is

port( clk,x,pre0,pre1 : in bit; q0,q1,z : out bit);

end circ_2;

architecture circ_2_archi of circ_2 is

--!--!--! OR COMPONENT --!--!--!

component orcom

port( a,b : in bit; c : out bit);

end component;

for all : orcom use entity work.orgate(orarchi);

--!--!--! AND(2-INPUT)COMPONENT --!--!--!

component and2com

port( a,b : in bit; c : out bit);

end component;

for all : and2com use entity work.andgate2(andarchi2);

--!--!--! AND(3-INPUT)COMPONENT --!--!--!

component and3com

port( a,b,c : in bit; d : out bit);

end component;

for all: and3com use entity work.andgate3(andarchi3);

--!--!--! INVERTER COMPONENT --!--!--!

component invcom

port( a : in bit; b : out bit);

end component;

for all: invcom use entity work.inv(invarchi);

--!--!--! JK FLIP FLOP COMPONENT --!--!--!

component jkcom

port( clk,j,k : in bit; q : out bit);

end component;

for all: jkcom use entity work.jk(jkarchi);

signal s0,s1,s2,s3,s4,s5: bit;

begin

AND1 : and2com port map (s5,s0,s1);

OR1 : orcom port map (x,s5,s3);

OR2 : orcom port map (x,s2,s4);

INV1 : invcom port map (x,s0);

JK1 : jkcom port map (clk,s1,s3,s2);

JK2 : jkcom port map (clk,s4,s0,s5);

AND2 : and3com port map (s2,s5,x,z);

q1 <= s2;

q0 <= s5;

end circ_2_archi;

library IEEE;

use IEEE.std_logic_1164.all;

----- OR GATE -----

entity orgate is

port( a,b : in bit; c : out bit);

end orgate;

architecture orarchi of orgate is

begin

c <= a or b;

end orarchi;

----- AND GATE (2-INPUT) -----

entity andgate2 is

port( a,b : in bit; c : out bit);

end andgate2;

architecture andarchi2 of andgate2 is

begin

c <= a and b;

end andarchi2;

----- AND GATE (3-INPUT) -----

entity andgate3 is

port( a,b,c : in bit; d : out bit);

end andgate3;

architecture andarchi3 of andgate3 is

begin

d <= a and b and c;

end andarchi3;

----- INVERTER -----

entity inv is

port( a : in bit; b : out bit);

end inv;

architecture invarchi of inv is

begin

b <= not a;

end invarchi;

----- JK FLIP FLOP -----

entity jk is

port( clk,j,k : in bit; q : out bit);

end jk;

architecture jkarchi of jk is

begin

process(clk,j,k)

variable temp : bit;

begin

if(clk = '1' and clk'event) then

if(j = '0' and k = '0') then

temp := temp;

elsif(j = '0' and k = '1') then

temp := '0';

elsif(j = '1' and k = '0') then

temp := '1';

elsif(j = '1' and k = '1') then

temp := not temp;

end if;

q <= temp;

else

temp := temp;

end if;

end process;

end jkarchi;

--!--!--!--!--!---!--!--!--!--!

--! CIRCUIT PORT MAPPING --!--!

--!--!--!--!--!---!--!--!--!--!

entity circ_2 is

port( clk,x,pre0,pre1 : in bit; q0,q1,z : out bit);

end circ_2;

architecture circ_2_archi of circ_2 is

--!--!--! OR COMPONENT --!--!--!

component orcom

port( a,b : in bit; c : out bit);

end component;

for all : orcom use entity work.orgate(orarchi);

--!--!--! AND(2-INPUT)COMPONENT --!--!--!

component and2com

port( a,b : in bit; c : out bit);

end component;

for all : and2com use entity work.andgate2(andarchi2);

--!--!--! AND(3-INPUT)COMPONENT --!--!--!

component and3com

port( a,b,c : in bit; d : out bit);

end component;

for all: and3com use entity work.andgate3(andarchi3);

--!--!--! INVERTER COMPONENT --!--!--!

component invcom

port( a : in bit; b : out bit);

end component;

for all: invcom use entity work.inv(invarchi);

--!--!--! JK FLIP FLOP COMPONENT --!--!--!

component jkcom

port( clk,j,k : in bit; q : out bit);

end component;

for all: jkcom use entity work.jk(jkarchi);

signal s0,s1,s2,s3,s4,s5: bit;

begin

AND1 : and2com port map (s5,s0,s1);

OR1 : orcom port map (x,s5,s3);

OR2 : orcom port map (x,s2,s4);

INV1 : invcom port map (x,s0);

JK1 : jkcom port map (clk,s1,s3,s2);

JK2 : jkcom port map (clk,s4,s0,s5);

AND2 : and3com port map (s2,s5,x,z);

q1 <= s2;

q0 <= s5;

end circ_2_archi;