I am new to VHDL, but have some idea. I made this LFSR but don't know why it is stuck between the initial seed value and the other XOR value. I am working with Altera Quartus 16 Lite and ISim.

library ieee;

use ieee.std_logic_1164.all;

--creating a galois LFSR

entity LFSR is

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic --lfsr done

);

end entity LFSR;

architecture behavioral of LFSR is

signal temp_out : std_logic_vector(15 downto 0) := (0 => '1' ,others => '0'); --initial value as seed

signal temp_done : std_logic;

begin

process (clk, rst)

begin

if rising_edge (clk) then --module operates only when enabled

if (rst = '1') then

temp_out <= (0 => '1' ,others => '0');

temp_done <= '0';

elsif (en = '1') then

temp_out <= temp_out(15 downto 11) & (temp_out(10) xor temp_out(0)) & temp_out(9 downto 5) & (temp_out(4) xor temp_out(0)) & temp_out(3 downto 0);

--temp_out <= (temp_out(15) xor temp_out(0)) & (temp_out(14) xor temp_out(0)) & temp_out(13) & (temp_out(12) xor temp_out(0)) & temp_out(11 downto 4) & (temp_out(3) xor temp_out(0)) & temp_out(2 downto 0);

temp_done <= '1';

end if;

end if;

end process;

rdm_out <= temp_out(15 downto 0);

rdm_out_a <= temp_out(15 downto 8);

rdm_out_b <= temp_out(7 downto 0);

lfsr_Done <= temp_done;

end architecture behavioral;`

The commented out temp_out is actual feedback (taps are 16,15,13, and 4) as I checked with random taps but still no improvement.

And the testbench I used is this:

library ieee;

use ieee.std_logic_1164.all;

entity lfsr_tb is

end lfsr_tb;

architecture test_bench of lfsr_tb is

component LFSR

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic );

end component;

signal clk1: std_logic;

signal rst1: std_logic;

signal en1 : std_logic;

signal rdm_out1 : std_logic_vector(15 downto 0);

signal rdm_out_a1 : std_logic_vector(7 downto 0);

signal rdm_out_b1 : std_logic_vector(7 downto 0);

signal lfsr_Done1 : std_logic ;

begin

mapping: LFSR port map(

clk => clk1,

rst => rst1,

en => en1,

rdm_out => rdm_out1,

rdm_out_a => rdm_out_a1,

rdm_out_b => rdm_out_b1,

lfsr_Done => lfsr_Done1 );

clock: process

begin

clk1 <= '0'; wait for 10 ps;

clk1 <= '1'; wait for 10 ps;

end process;

reset: process

begin

rst1 <= '1'; wait for 10 ps;

rst1 <= '0';

en1 <= '1'; wait for 800 ps;

end process;

end test_bench;

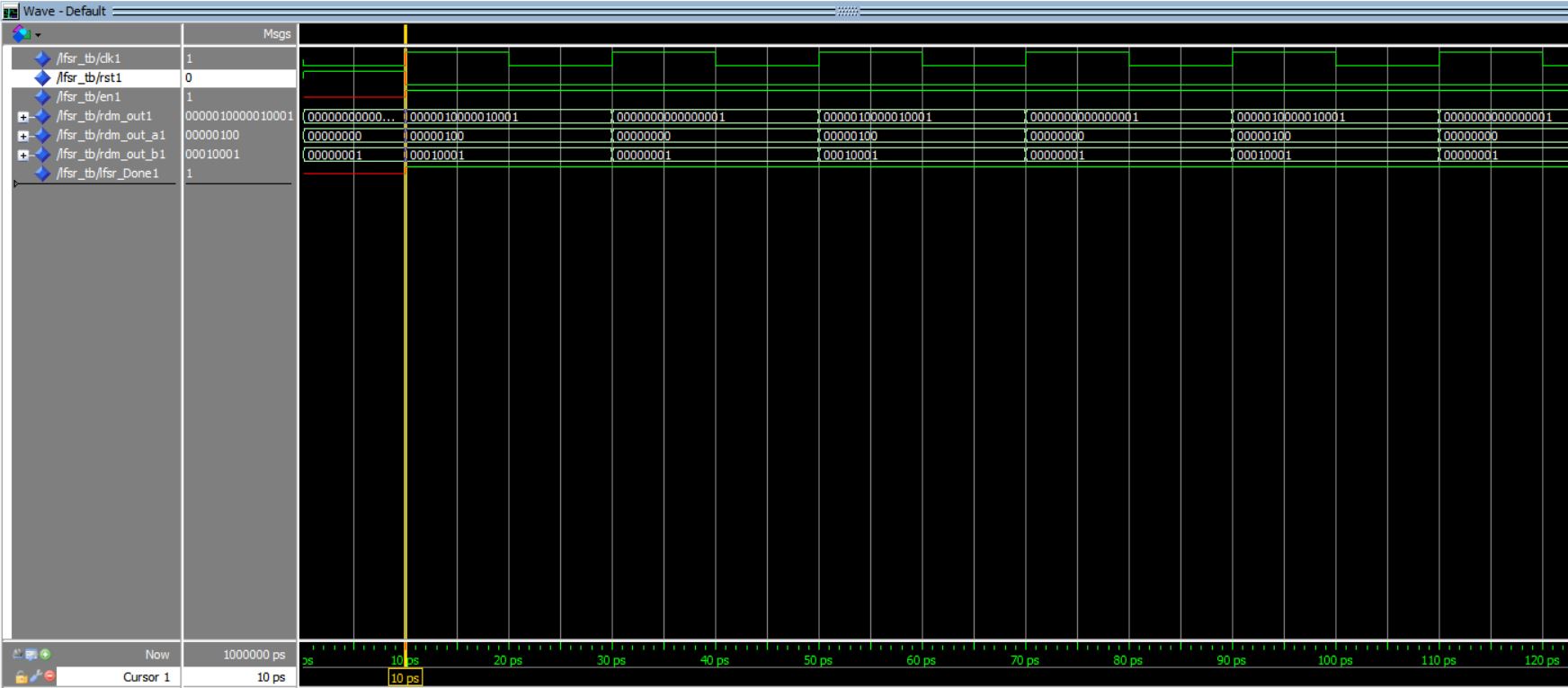

This is the result I am getting:

I have tried numerous ways but its not shifting and I don't understand why.

library ieee;

use ieee.std_logic_1164.all;

--creating a galois LFSR

entity LFSR is

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic --lfsr done

);

end entity LFSR;

architecture behavioral of LFSR is

signal temp_out : std_logic_vector(15 downto 0) := (0 => '1' ,others => '0'); --initial value as seed

signal temp_done : std_logic;

begin

process (clk, rst)

begin

if rising_edge (clk) then --module operates only when enabled

if (rst = '1') then

temp_out <= (0 => '1' ,others => '0');

temp_done <= '0';

elsif (en = '1') then

temp_out <= temp_out(15 downto 11) & (temp_out(10) xor temp_out(0)) & temp_out(9 downto 5) & (temp_out(4) xor temp_out(0)) & temp_out(3 downto 0);

--temp_out <= (temp_out(15) xor temp_out(0)) & (temp_out(14) xor temp_out(0)) & temp_out(13) & (temp_out(12) xor temp_out(0)) & temp_out(11 downto 4) & (temp_out(3) xor temp_out(0)) & temp_out(2 downto 0);

temp_done <= '1';

end if;

end if;

end process;

rdm_out <= temp_out(15 downto 0);

rdm_out_a <= temp_out(15 downto 8);

rdm_out_b <= temp_out(7 downto 0);

lfsr_Done <= temp_done;

end architecture behavioral;`

The commented out temp_out is actual feedback (taps are 16,15,13, and 4) as I checked with random taps but still no improvement.

And the testbench I used is this:

library ieee;

use ieee.std_logic_1164.all;

entity lfsr_tb is

end lfsr_tb;

architecture test_bench of lfsr_tb is

component LFSR

port (

clk : in std_logic;

rst : in std_logic;

en : in std_logic;

rdm_out : out std_logic_vector(15 downto 0);

rdm_out_a : out std_logic_vector(7 downto 0);

rdm_out_b : out std_logic_vector(7 downto 0);

lfsr_Done : out std_logic );

end component;

signal clk1: std_logic;

signal rst1: std_logic;

signal en1 : std_logic;

signal rdm_out1 : std_logic_vector(15 downto 0);

signal rdm_out_a1 : std_logic_vector(7 downto 0);

signal rdm_out_b1 : std_logic_vector(7 downto 0);

signal lfsr_Done1 : std_logic ;

begin

mapping: LFSR port map(

clk => clk1,

rst => rst1,

en => en1,

rdm_out => rdm_out1,

rdm_out_a => rdm_out_a1,

rdm_out_b => rdm_out_b1,

lfsr_Done => lfsr_Done1 );

clock: process

begin

clk1 <= '0'; wait for 10 ps;

clk1 <= '1'; wait for 10 ps;

end process;

reset: process

begin

rst1 <= '1'; wait for 10 ps;

rst1 <= '0';

en1 <= '1'; wait for 800 ps;

end process;

end test_bench;

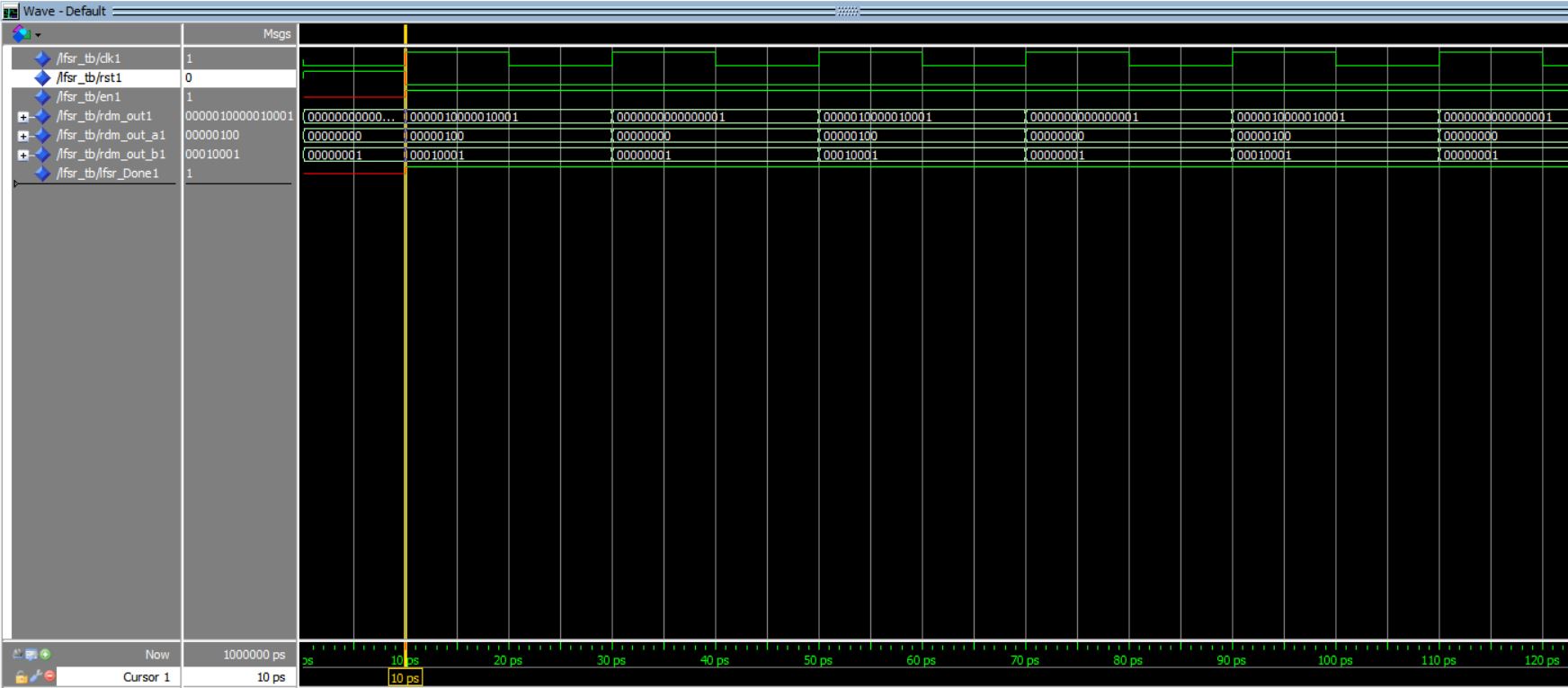

This is the result I am getting:

I have tried numerous ways but its not shifting and I don't understand why.